# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

#### PRELIMINARY

# ADXL356/ADXL357

#### **FEATURES**

Ultralow noise density: 80µg/√Hz Resonant frequency of 5.4kHz

Offset temperature coefficient of <0.75mg/°C (max) with minimal hysteresis

Hermetic package offers excellent long-term stability Low power:

200 μA in measurement mode (digital) 175 μA in measurement mode (analog) 30 μA in standby mode

Digital SPI/I<sup>2</sup>C interfaces

20-Bit ADC

Data interpolation routine for synchronous sampling Programmable high- and low-pass filters

Analog interface

Bandwidth set with external capacitor

Electromechanical self-test

Integrated temperature sensor

Supply voltage options:

2.25 V to 3.6 V with internal regulators

Or 1.8 V ± 10%

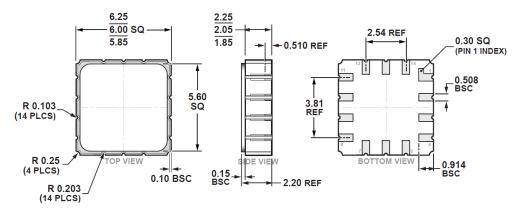

Operating Temperature Range: -40°C to 125°C 6 mm × 6 mm × 2.1 mm 14-pin hermetic, 0.26grams ceramic package

#### **APPLICATIONS**

IMU/AHRS Stabilization systems Tilt sensing Robotics Condition Monitoring

#### **GENERAL DESCRIPTION**

The ADXL356 (analog output) ADXL357 (digital output) are low noise density, high frequency, low 0-g offset drift, low power, 3-axis accelerometers with selectable measurement ranges up to  $\pm 40~g$ , helping to prevent saturation in a high shock and vibration environment. The ADXL356/357 offers industry-leading noise density over a wide frequency band, with a resonance of 5.4kHz

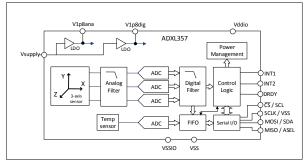

Figure 1: ADXL357 Functional Block Diagram.

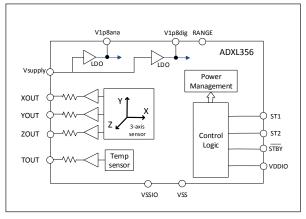

Figure 2: ADXL356 Functional Block Diagram.

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

# ADXL356/ADXL357

#### TABLE OF CONTENTS

| Features                                          | 1  |

|---------------------------------------------------|----|

| Applications                                      | 1  |

| General Description                               | 1  |

| Specifications                                    | 4  |

| Absolute Maximum Ratings                          | 10 |

| ESD caution                                       | 10 |

| Acceleration Sensitive AxEs                       | 10 |

| Pin Configuration and Function Descriptions       | 11 |

| Typical Performance Charts                        | 13 |

| ADXL 356 (Analog output)                          | 13 |

| ADXL 357 (DIGITAL output)                         | 14 |

| Application Information                           | 15 |

| Theory of Operation                               | 15 |

| Digital Output                                    | 15 |

| Analog Output                                     | 15 |

| Power Sequencing                                  | 16 |

| Power Supply Description                          | 16 |

| Over-Range Protection                             | 16 |

| Self Test                                         | 16 |

| Serial Communication                              | 20 |

| SPI Protocol                                      | 20 |

| I2C Protocol                                      | 22 |

| Reading Acceleration or Temperature Data from the |    |

| Interface                                         |    |

| FIFO                                              |    |

| Interrupts                                        |    |

| External Sync and Interpolation                   |    |

| ADXL357 Register Map                              |    |

| Register Definitions                              |    |

| Analog Devices ID Register                        |    |

| Analog Devices MEMS ID Register                   |    |

| Device ID Register                                |    |

| Product Revision ID Register                      | 30 |

| Status Register                                   | 30 |

| FIFO Entries Registers                           | 31  |

|--------------------------------------------------|-----|

| Temperature Data Registers                       | 31  |

| X-Axis Data Registers                            | 31  |

| Y-Axis Data Registers                            | 32  |

| Z-Axis Data Registers                            | 32  |

| FIFO Access Register                             | 33  |

| X-Axis Offset Trim Registers                     | 33  |

| Y-Axis Offset Trim Registers                     | 33  |

| Z-Axis Offset Trim Registers                     | 34  |

| Activity Enable Register                         | 34  |

| Activity Threshold Registers                     | 34  |

| Activity Count Register                          | 35  |

| Filter Settings Register                         | 35  |

| FIFO Samples Register                            | 35  |

| Interrupt Pin Function Map Register              | 36  |

| Data Synchronization                             | 36  |

| I2C Speed, Interrupt Polarity and Range Register | r36 |

| Power Control Register                           | 37  |

| Self-Test Register                               | 37  |

| Reset Register                                   | 37  |

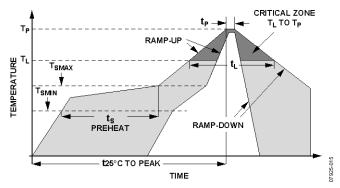

| Recommended Soldering Profile                    | 38  |

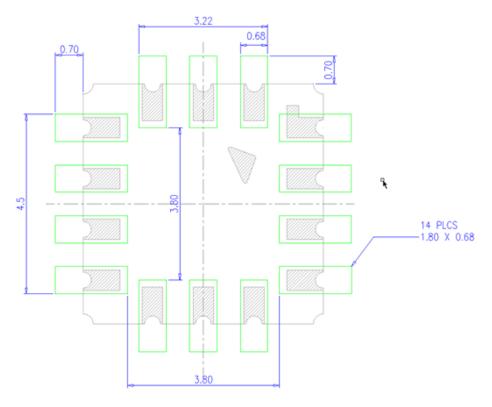

| PCB Footprint Pattern                            | 39  |

| Outline Dimensions                               | 40  |

|                                                  |     |

Ordering Guide ......40

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. See the last page for disclaimers.

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

ADXL356/ADXL357

#### **SPECIFICATIONS**

$T_A = 25$ °C,  $V_{SUPPLY} = 3.3$  V, acceleration = 0 g, Output Data Rate = 125Hz.

Table 1: ADXL357 (DIGITAL OUTPUT)

| Parameter                                                               | Test Conditions                                                                             | Min <sup>2</sup> | Typ¹  | Max   | Unit            |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------|-------|-------|-----------------|

| SENSOR INPUT                                                            | Each axis                                                                                   |                  |       |       |                 |

| Output Full Scale Range (FSR)                                           | User selectable                                                                             |                  | ±10   |       | g               |

|                                                                         |                                                                                             |                  | ±20   |       |                 |

|                                                                         |                                                                                             |                  | ±40   |       |                 |

| Nonlinearity <sup>1</sup>                                               | ±10 <i>g</i>                                                                                |                  | 0.1   |       | %               |

| Cross-Axis Sensitivity                                                  |                                                                                             |                  | 1     |       | %               |

| SENSITIVITY                                                             | Each axis                                                                                   |                  |       |       |                 |

| Sensitivity at Xout, Yout, Zout                                         | ±10 g                                                                                       | 47104            | 51200 | 55296 | LSB/g           |

|                                                                         | ±20 g                                                                                       | 23552            | 25600 | 27648 | LSB/g           |

|                                                                         | ±40 <i>g</i>                                                                                | 11776            | 12800 | 13824 | LSB/g           |

| Scale Factor at X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub>  | ±10 g                                                                                       |                  | 40    |       | μ <i>g/</i> LSB |

|                                                                         | ±20 g                                                                                       |                  | 39    |       | μ <i>g/</i> LSB |

|                                                                         | ±40 <i>g</i>                                                                                |                  | 78    |       | μ <i>g/</i> LSB |

| Sensitivity Change Due to Temperature                                   | -40°C to 105°C                                                                              |                  | ±0.01 |       | %/°C            |

| Sensitivity Change Due to Temperature                                   | -40°C to 125°C                                                                              |                  | ±TBD  |       | %/°C            |

| Repeatability Error! Bookmark not defined.                              |                                                                                             |                  | ±TBD  |       | %               |

| o g OFFSET                                                              | Each axis, ±10 g                                                                            |                  |       |       |                 |

| o $g$ Output for X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub> |                                                                                             | -150             | ±25   | +150  | m <i>g</i>      |

| o $g$ Offset vs. Temperature (XYZ axes) $^{\scriptscriptstyle 2}$       | -40°C to 105°C                                                                              | -0.75            | ±0.02 | 0.75  | m <i>g</i> /°C  |

| o $g$ Offset vs. Temperature (XYZ axes) $^{\scriptscriptstyle 2}$       | -40°C to 125°C                                                                              | -TBD             | ±TBD  | TBD   | m <i>g</i> /°C  |

| Repeatability <sup>3</sup>                                              |                                                                                             |                  | ±25   |       | m <i>g</i>      |

| Vibration Rectification                                                 | ±40 g range, offset<br>shift under 10g rms<br>50Hz to 2kHz<br>random vibration,<br>4kHz ODR |                  | TBD   |       | g               |

| NOISE                                                                   | ±10 g                                                                                       |                  |       |       |                 |

| X, Y, Z Axes                                                            |                                                                                             |                  | 80    |       | μ <i>g</i> /√Hz |

| Velocity Random Walk                                                    |                                                                                             |                  | TBD   |       | μm/s/√hr        |

| OUTPUT DATA RATE AND BANDWIDTH                                          | User Selectable                                                                             |                  |       |       |                 |

| Bandwidth                                                               |                                                                                             |                  |       |       |                 |

| Low Pass Filter -3 dB Frequency                                         |                                                                                             |                  | 11000 |       | Hz              |

| High Pass Filter -3 dB Frequency                                        |                                                                                             |                  | DC 10 |       | Hz              |

¹ The typical specifications shown are for at least 68% of the population of parts and are based on the worst case of mean ±1 of, except for sensitivity, which represents the

#### Rev PrD

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. See the last page for disclaimers.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106,

U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>2</sup> Min/Max is determined by characterization and represents 99.97% of the population.

$_3$  Includes shifts due to HTOL (TA = 150°C, Vs = 3.6V, 1000hrs) and Temperature Cycling (-55°C to 125°C, 1000 cycles).

| Parameter                                      | Test Conditions                                                       | Min <sup>2</sup> | Typ¹  | Max  | Unit   |

|------------------------------------------------|-----------------------------------------------------------------------|------------------|-------|------|--------|

| Output Data Rate to Bandwidth Ratio            |                                                                       |                  | 4     |      |        |

| SELF-TEST                                      |                                                                       |                  |       |      |        |

| Output Change in X-Axis                        |                                                                       |                  | 0.3   |      | g      |

| Output Change in Y-Axis                        |                                                                       |                  | 0.3   |      | g      |

| Output Change in Z-Axis                        |                                                                       |                  | 1.5   |      | g      |

| POWER SUPPLY                                   |                                                                       |                  |       |      |        |

| Operating Voltage Range (V <sub>SUPPLY</sub> ) |                                                                       | 2.25             | 2.5   | 3.6  | V      |

| I/O Voltage Range (V <sub>DDI/O</sub> )        |                                                                       | V1p8dig          | 2.5   | 3.6  | V      |

| Operating Voltage with Internal LDO bypassed   | V <sub>SUPPLY</sub> = oV                                              | 1.62             | 1.8   | 1.98 | V      |

| Supply Current                                 |                                                                       |                  | 200   |      | μΑ     |

| Standby Mode Current                           |                                                                       |                  | 30    |      | μΑ     |

| Turn-On Time                                   | Standby to measurement mode (to within 1mg of final value, 1og range) |                  | <10   |      | ms     |

|                                                | Power-off to standby                                                  |                  | <10   |      | ms     |

| TEMPERATURE SENSOR                             |                                                                       |                  |       |      |        |

| Output at 25°C                                 |                                                                       |                  | 1852  |      | LSB    |

| Long term stability <sup>3</sup>               |                                                                       |                  | TBD   |      | °C     |

| Scale Factor                                   |                                                                       |                  | -9.05 |      | LSB/°C |

| TEMPERATURE                                    |                                                                       |                  |       |      |        |

| Operating Temperature Range                    |                                                                       | -40              |       | +125 | °C     |

$T_A = 25$ °C,  $V_{SUPPLY} = 3.3$  V, acceleration = 0g.

Table 2: ADXL356 (ANALOG OUTPUT)

| Parameter                                                                     | Test Conditions                                                                             | Min     | Typ¹     | Max  | Unit           |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|----------|------|----------------|

| SENSOR INPUT                                                                  | Each axis                                                                                   |         |          |      |                |

| Output Full Scale Range (FSR)                                                 | ADXL <sub>35</sub> 6B                                                                       |         | ±10, ±20 |      | g              |

|                                                                               | ADXL <sub>35</sub> 6C                                                                       |         | ±10, ±40 |      | g              |

| Nonlinearity <sup>1</sup>                                                     | ±10 g                                                                                       |         | 0.1      |      | %              |

| Cross-Axis Sensitivity                                                        |                                                                                             |         | 1        |      | %              |

| SENSITIVITY                                                                   | Ratiometric to<br>V1p8ana                                                                   |         |          |      |                |

| Sensitivity at X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub>         | ±10 g                                                                                       | 73.6    | 80       | 86.4 | mV/g           |

|                                                                               | ±20 g                                                                                       | 36.8    | 40       | 43.2 | mV/g           |

|                                                                               | ±40 g                                                                                       | 18.4    | 20       | 21.6 | mV/g           |

| Sensitivity Change Due to Temperature                                         | -40°C to 105°C                                                                              |         | ±0.01    |      | %/°C           |

| Sensitivity Change Due to Temperature                                         | -40°C to 125°C                                                                              |         | ±TBD     |      | %/°C           |

| Repeatability <sup>3</sup>                                                    |                                                                                             |         | 0.125    |      | %              |

| o g OFFSET                                                                    | Each axis, ±2 g                                                                             |         |          |      |                |

| о g Output for Х <sub>оит</sub> , Y <sub>оит</sub> , Z <sub>оит</sub>         | Referred to V1p8ana/2                                                                       | -150    | ±25      | +150 | m <i>g</i>     |

| o $g$ Offset vs. Temperature (XYZ axes) Error! Bookmark not defined.          | -40°C to 105°C                                                                              | -0.75   | ±0.1     | 0.75 | m <i>g</i> /°C |

| o g Offset vs. Temperature (XYZ axes) <sup>Error!</sup> Bookmark not defined. | -40°C to 125°C                                                                              | -TBD    | ±TBD     | TBD  | m <i>g</i> /°C |

| Repeatability Error! Bookmark not defined.                                    |                                                                                             |         | ±5       |      | m <i>g</i>     |

| Vibration Rectification                                                       | ±40 g range, offset<br>shift under 10g rms<br>50Hz to 2kHz<br>random vibration,<br>4kHz ODR |         | TBD      |      | g              |

| NOISE                                                                         | ±10 g                                                                                       |         |          |      |                |

| X, Y, Z Axes                                                                  |                                                                                             |         | 80       |      | μg/√Hz         |

| Velocity Random Walk                                                          |                                                                                             |         | TBD      |      | μm/s/√hi       |

| BANDWIDTH                                                                     |                                                                                             |         |          |      |                |

| LPF ±3 dB Frequency                                                           | Set by external capacitors                                                                  |         | 11000    |      | Hz             |

| SELF-TEST                                                                     |                                                                                             |         |          |      |                |

| Output Change in X-Axis                                                       |                                                                                             |         | 0.3      |      | g              |

| Output Change in Y-Axis                                                       |                                                                                             |         | 0.3      |      | g              |

| Output Change in Z-Axis                                                       |                                                                                             |         | 1.5      |      | g              |

| POWER SUPPLY                                                                  |                                                                                             |         |          | 6    |                |

| Operating Voltage Range (V <sub>SUPPLY</sub> )                                |                                                                                             | 2.25    | 2.5      | 3.6  | V              |

| I/O Voltage Range (V <sub>DDI/O</sub> )                                       |                                                                                             | V1p8dig | 2.5      | 3.6  | V              |

| Operating Voltage with Internal LDO bypassed                                  | V <sub>SUPPLY</sub> = 0V                                                                    | 1.62    | 1.8      | 1.98 |                |

| Supply Current                                                                |                                                                                             |         | 175      |      | μΑ             |

| Turn-On Time                                                                  | Standby to measurement mode (to within                                                      |         | <10      |      | ms             |

<sup>&</sup>lt;sup>1</sup> The typical specifications shown are for at least 68% of the population of parts and are based on the worst case of mean ±1 σ, except for sensitivity, which represents the target value.

<sup>&</sup>lt;sup>2</sup> Min/Max is determined by characterization and represents 99.97% of the population.

$<sup>^3</sup>$  Includes shifts due to HTOL (T<sub>A</sub> = 150°C, V<sub>S</sub> = 3.6V, 1000hrs) and Temperature Cycling (-55°C to 125°C, 1000 cycles).

| Parameter                        | Test Conditions     | Min  | Typ¹  | Max            | Unit  |

|----------------------------------|---------------------|------|-------|----------------|-------|

|                                  | 1mg of final value, |      |       |                |       |

|                                  | 10g range)          |      |       |                |       |

|                                  | Power-off to        |      | <10   |                | ms    |

|                                  | standby             |      |       |                |       |

| OUTPUT AMPLIFIER                 |                     |      |       |                |       |

| Swing                            | No load             | 0.03 |       | V1p8ana – o.o3 | ٧     |

| Output Resistance                |                     |      | 32    |                | kΩ    |

| TEMPERATURE SENSOR               |                     |      |       |                |       |

| Output at 25°C                   |                     |      | 892.2 |                | mV    |

| Scale Factor                     |                     |      | 3     |                | mV/C  |

| Long term stability <sup>3</sup> |                     |      | TBD   |                | °C    |

| Scale Factor                     |                     |      | 3.0   |                | mV/°C |

| TEMPERATURE                      |                     |      |       |                |       |

| Operating Temperature Range      |                     | -40  |       | +125           | °C    |

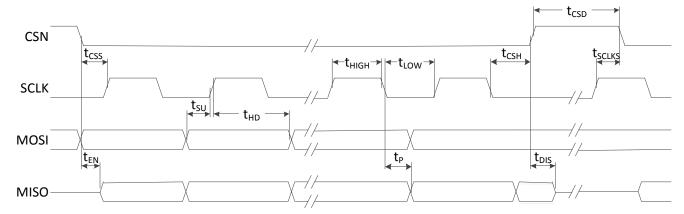

Figure 3 SPI Interface Timing Parameters

### Table 3 ADXL357 SPI DIGITAL INTERFACE CHARACTERISTICS

| Parameter                      | Description                                                     | Min                   | Typ¹ | Max                   | Unit |

|--------------------------------|-----------------------------------------------------------------|-----------------------|------|-----------------------|------|

| INPUT DC LEVELS                |                                                                 |                       |      |                       |      |

| $V_{IL}$                       | Low level input voltage                                         |                       |      | 0.3*V <sub>DDIO</sub> | V    |

| $V_{IH}$                       | High level input voltage                                        | o.7*V <sub>DDIO</sub> |      |                       | V    |

| I <sub>IL</sub>                | Low level input current, V <sub>IN</sub> =oV                    | -0.1                  |      |                       | μΑ   |

| I <sub>IH</sub>                | High level input current, V <sub>IN</sub> =V <sub>DDIO</sub>    |                       |      | 0.1                   | μΑ   |

| OUTPUT DC LEVELS               |                                                                 |                       |      |                       |      |

| $V_{OL}$                       | Low level output voltage, IoL=IoL,Min                           |                       |      | $0.2*V_{DDIO}$        | V    |

| V <sub>OH</sub>                | High level output voltage, IoL=IOH,Max                          | o.8*V <sub>DDIO</sub> |      |                       | V    |

| I <sub>OL</sub>                | Low level output current, V <sub>OL</sub> =V <sub>OL,Max</sub>  | -10mA                 |      |                       | mA   |

| I <sub>OH</sub>                | High level output current, V <sub>OL</sub> =V <sub>OH,Min</sub> |                       |      | 4mA                   | mA   |

| INPUT AC Parameters            |                                                                 |                       |      |                       |      |

| SCLK Frequency                 |                                                                 | О                     |      | 10                    | MHz  |

| t <sub>HIGH</sub>              | SCLK high time                                                  | 40                    |      |                       | nsec |

| t <sub>LOW</sub> SCLK low time |                                                                 | 40                    |      |                       | nsec |

| t <sub>CSS</sub>               | CSN set-up time 20                                              |                       |      |                       | nsec |

| t <sub>CSH</sub>               | CSN hold time                                                   | 20                    |      |                       | nsec |

# ADXL356/ADXL357

| Parameter            | Description                                | Min  | Typ¹ | Max  | Unit |

|----------------------|--------------------------------------------|------|------|------|------|

| t <sub>CSD</sub>     | CSN disable time                           | 40   |      |      | nsec |

| t <sub>SCLKS</sub>   | Rising SCLK setup time                     | 20   |      |      | nsec |

| $t_{SU}$             | MOSI setup time                            | 20   |      | nsec |      |

| t <sub>HD</sub>      | MOSI hold time                             | 20   |      |      | nsec |

| OUTPUT AC Parameters |                                            |      |      |      |      |

| $t_P$                | Propagation delay, C <sub>LOAD</sub> =30pF |      |      | 30   | nsec |

| t <sub>EN</sub>      | Enable MISO time 30                        |      | nsec |      |      |

| t <sub>DIS</sub>     | Disable MISO time                          | 20 n |      | nsec |      |

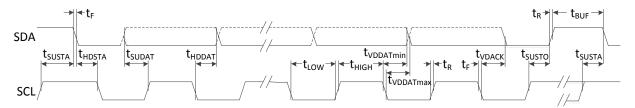

Figure 4 I2C Interface Timing Parameters

#### Table 4 I2C DIGITAL INTERFACE CHARACTERISTICS

|                        |                                                                                  | I2C_HS=o               |      |                | I2C_HS=1              |      |                |      |

|------------------------|----------------------------------------------------------------------------------|------------------------|------|----------------|-----------------------|------|----------------|------|

| Parameter              | Description                                                                      | Min                    | Typ¹ | Max            | Min                   | Typ² | Max            | Unit |

| INPUT DC<br>LEVELS     |                                                                                  |                        |      |                |                       |      |                |      |

| $V_{IL}$               | Low level input voltage                                                          |                        |      | $0.3*V_{DDIO}$ |                       |      | $0.3*V_{DDIO}$ | V    |

| $V_{IH}$               | High level input voltage                                                         | o.7*V <sub>DDIO</sub>  |      |                | 0.7*V <sub>DDIO</sub> |      |                | V    |

| $V_{HYS}$              | Hysteresis of Schmitt trigger inputs                                             | 0.05*V <sub>DDIO</sub> |      |                | 0.1*V <sub>DDIO</sub> |      |                | μΑ   |

| I <sub>IL</sub>        | Input current, 0.1x V <sub>DDIO</sub> <v<sub>IN&lt;0.9 xV<sub>DDIO</sub></v<sub> | -10                    |      | 10             |                       |      |                | μА   |

| OUTPUT DC<br>LEVELS    |                                                                                  |                        |      |                |                       |      |                |      |

| $V_{OL_1}$             | Low level output voltage,<br>I <sub>OL</sub> =3mA, V <sub>DD</sub> >2V           |                        |      | 0.4            |                       |      |                | V    |

| $V_{OL_2}$             | Low level output voltage,                                                        |                        |      | $0.2*V_{DDIO}$ |                       |      |                | V    |

|                        | I <sub>OL</sub> =3mA, V <sub>DD</sub> <=2V                                       |                        |      |                |                       |      |                |      |

| I <sub>OL</sub>        | Low level output current,                                                        | 20mA                   |      |                |                       |      |                | mA   |

|                        | V <sub>OL</sub> =0.4V<br>Low level output current,<br>V <sub>OL</sub> =0.6V      | 6mA                    |      |                |                       |      |                | mA   |

| INPUT AC<br>Parameters |                                                                                  |                        |      |                |                       |      |                |      |

| SCLK<br>Frequency      |                                                                                  | 0                      |      | 1              | 0                     |      | 3.4            | MHz  |

| t <sub>HIGH</sub>      | SCLK high time                                                                   | 260                    |      |                | 60                    |      |                | nsec |

| $t_{LOW}$              | SCLK low time                                                                    | 500                    |      |                | 160                   |      |                | nsec |

| t <sub>SUSTA</sub>     | Start set-up time                                                                | 260                    |      |                | 160                   |      |                | nsec |

| t <sub>HDSTA</sub>     | Start hold time                                                                  | 260                    |      |                | 160                   |      |                | nsec |

| $t_{SUDAT}$            | Data set-up time                                                                 | 50                     |      |                | 10                    |      |                | nsec |

| $t_{HDDAT}$            | Data hold time                                                                   | 0                      |      |                | 0                     |      |                | nsec |

# ADXL356/ADXL357

|                         |                                                      |                           | I2C_HS=0 |     |     | I2C_HS= | 1   |      |

|-------------------------|------------------------------------------------------|---------------------------|----------|-----|-----|---------|-----|------|

| Parameter               | Description                                          | Min                       | Typ¹     | Max | Min | Typ²    | Max | Unit |

| t <sub>SUSTO</sub>      | Stop setup time                                      | 260                       |          |     | 160 |         |     | nsec |

| $t_{BUF}$               | Bus free time                                        | 500                       |          |     | -   |         |     | nsec |

| $t_{RCL}$               | SCL input rise time                                  |                           |          | 120 |     |         | 160 | nsec |

| $t_{FCL}$               | SCL input fall time                                  |                           |          | 120 |     |         | 80  | nsec |

| $t_{RDA}$               | SDA input rise time                                  |                           |          | 120 |     |         | 160 | nsec |

| $t_{FDA}$               | SDA input fall time                                  |                           |          | 120 |     |         | 160 | nsec |

| $t_SP$                  | Width of spikes to be supressed                      |                           |          | 50  |     |         | 10  | nsec |

| OUTPUT AC<br>Parameters |                                                      |                           |          |     |     |         |     |      |

| t <sub>VDDAT</sub>      | Data propagation delay,<br>C <sub>LOAD</sub> =550pF? | 97                        |          | 450 | 27  |         | 135 | nsec |

| tvdack                  | ACK propagation delay, C <sub>LOAD</sub> =550pF?     |                           |          | 450 |     |         | -   | nsec |

| $t_{F}$                 | Output fall time                                     | 20x(V <sub>DD</sub> /5.5) |          | 120 |     |         | TBD | nsec |

#### ABSOLUTE MAXIMUM RATINGS

#### Table 5.

| Tubic 5.                                 |                                    |

|------------------------------------------|------------------------------------|

| Parameter                                | Rating                             |

| Acceleration (Any Axis, Unpowered, 0.5   | TBD                                |

| ms)                                      |                                    |

| Acceleration (Any Axis, Powered, o.5 ms) | TBD                                |

| V <sub>SUPPLY</sub> , V <sub>DDIO</sub>  | 3.6 V                              |

| All other pins                           | TBD                                |

| Output Short-Circuit Duration            | TBD                                |

| (Any Pin to Common)                      |                                    |

| Operating Temperature Range              | -40°C to +125°C                    |

| Storage Temperature                      | -40°C to +125°C<br>-65°C to +150°C |

|                                          |                                    |

Stresses above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification (Table 1, Table 2) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

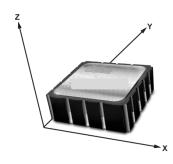

#### **ACCELERATION SENSITIVE AXES**

Figure 5. Axes of Acceleration Sensitivity (Corresponding Output Voltage Increases When Accelerated Along the Sensitive Axis)

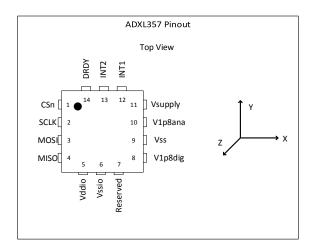

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. ADXL357 Pin Configuration (top view)

Table 6: ADXL357 Pin Function Descriptions

| Pin No. | Pin Name         | Description                                                                             |

|---------|------------------|-----------------------------------------------------------------------------------------|

| 1       | CSn/SCL          | SPI: Chip Select                                                                        |

|         |                  | I2C: Serial Communications Clock                                                        |

| 2       | SCLK/Vssio       | SPI: Serial Communications Clock                                                        |

|         |                  | I <sub>2</sub> C: Connect to Vssio                                                      |

| 3       | MOSI/SDA         | SPI: Master Output Slave Input                                                          |

|         |                  | I2C: Serial Data                                                                        |

| 4       | MISO/ASEL        | SPI: Master Input Slave Output                                                          |

|         |                  | I2C: Alternate I2C Address Select                                                       |

| 5       | Vddio            | Digital Interface Supply Voltage                                                        |

| 6       | Vssio            | Digital Ground                                                                          |

| 7       | Reserved         | This pin can be connected to ground or left open                                        |

| 8       | V1p8dig          | Internal Logic supply. Needs bypass cap. Must be driven if Vsupply is connected to Vss. |

| 9       | Vss              | Analog ground                                                                           |

| 10      | V1p8ana          | Analog supply. Needs bypass cap. Must be driven if Vsupply is connected to Vss.         |

| 11      | Vsupply          | 2.25 - 3.6V                                                                             |

|         |                  | For Vdd = 2.25-3.6V, V1p8dig, V1p8ana are regulator outputs                             |

|         |                  | For Vdd = oV, V1p8dig, V1p8ana are 1.62-1.98V supply inputs                             |

| 12      | INT1             | Interrupt Pin                                                                           |

| 13      | INT <sub>2</sub> | Interrupt Pin                                                                           |

| 14      | DRDY             | Interrupt Pin                                                                           |

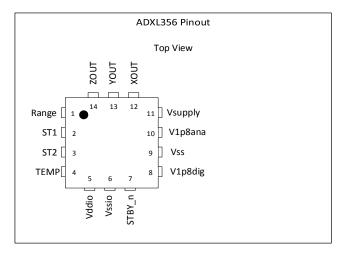

Figure 7. ADXL356 Pin Configuration (top view)

**Table 7: ADXL356 Pin Function Descriptions**

| Pin No. | Pin Name        | Description                                                                             |

|---------|-----------------|-----------------------------------------------------------------------------------------|

| 1       | Range           | Range Selection Pin                                                                     |

|         |                 | Set to ground to select ±2g range                                                       |

|         |                 | Set to Vddio to select $\pm 4g$ or $\pm 8g$ range (model dependent. See ordering guide) |

| 2       | ST <sub>1</sub> | Self-Test Pin                                                                           |

| 3       | ST <sub>2</sub> | Self-Test Pin                                                                           |

| 4       | Tout            | Temperature Sensor Output                                                               |

| 5       | Vddio           | Digital Interface Supply Voltage                                                        |

| 6       | Vssio           | Digital Ground.                                                                         |

| 7       | STBY_n          | Select standby or measurement mode                                                      |

|         |                 | Set to ground to enter standby mode                                                     |

|         |                 | Set to Vddio to enter measurement mode                                                  |

| 8       | V1p8dig         | Internal Logic supply. Needs bypass cap. Must be driven if Vsupply is                   |

|         |                 | connected to Vss.                                                                       |

| 9       | Vss             | Analog Ground                                                                           |

| 10      | V1p8ana         | Analog supply. Needs bypass cap. Must be driven if Vsupply is connected to Vss.         |

| 11      | Vsupply         | 2.25 - 3.6V                                                                             |

|         |                 | For Vsupply = 2.25-3.6V, V1p8dig, V1p8ana are regulator outputs.                        |

|         |                 | For Vsupply = oV, V1p8dig, V1p8ana are 1.62-1.98V supply inputs.                        |

| 12      | Xout            | X-axis output                                                                           |

| 13      | Yout            | Y-axis output                                                                           |

| 14      | Zout            | Z-axis output                                                                           |

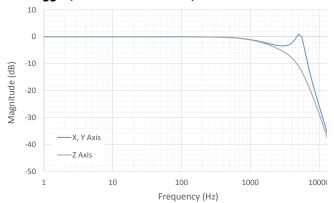

## TYPICAL PERFORMANCE CHARTS

## **ADXL 356 (ANALOG OUTPUT)**

Figure 8ADXL356 frequency response

## **ADXL 357 (DIGITAL OUTPUT)**

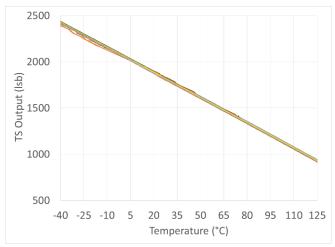

Figure 9 Temperature sensor output vs temperature (N=15)

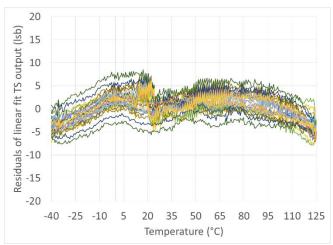

Figure 10 Residuals of linear fit to temperature sensor output vs temperature (N=15)

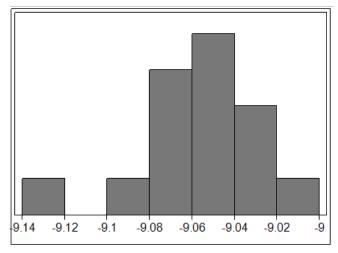

Figure 11 Temperature sensor scale factor in LSB/°C (N=15)

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

# ADXL356/ADXL357

# APPLICATION INFORMATION

#### THEORY OF OPERATION

The ADXL356 is a complete 3-axis ultra-low noise and ultra-stable offset accelerometer with outputs ratiometric to the analog 1.8V supply. The ADXL357 adds three high resolution ADCs which use the analog 1.8V supply as a reference to provide digital outputs insensitive to supply voltage. The ADXL356B is pinselectable for  $\pm 10$ g or  $\pm 20$ g full scale, and the ADXL356C is pin-selectable for  $\pm 10$ g or  $\pm 40$ g full scale. The ADXL357 is programmable for  $\pm 10$ g,  $\pm 20$ g or  $\pm 40$ g full scale. The ADXL357 offers both SPI and I2C communications ports.

The surface-micromachined sensing elements are fully differential, comprising lateral XY-axis sensors and vertical teeter-totter Z-axis sensors. The XY sensors and the Z sensors go through separate signal paths, which have been designed to minimize offset drift and noise. The signal path is fully differential, except for a differential to single-ended conversion at the analog outputs.

The analog accelerometer outputs of the ADXL356 are ratiometric to V1p8ana, so careful attention must be taken to digitize them correctly. The temperature sensor output is not ratiometric. All analog outputs include an internal  $32k\Omega$  resistor which can be used with a user-supplied external capacitor to set the bandwidth of the anti-alias filter.

The ADXL357 includes appropriate anti-alias filters before the ADC. User selectable output data rates and filter corners are provided. The temperature sensor is digitized with a 12-bit SAR converter.

#### **DIGITAL OUTPUT**

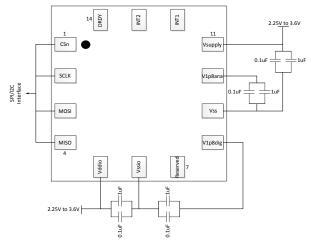

The ADXL357 application circuit is shown in Figure 12 with the recommended bypass capacitors. The communications interface is either SPI or I2C. See Serial Communication section for further details.

Figure 12. ADXL357 Application Circuit

The ADXL357 includes an internal configurable bandpass filter. Both the high- and low-pass poles of the filter are adjustable as shown in the Register Definition section under Filter Settings register. At power-up, the default condition for the filters is HPF = DC and LPF =  $1000 \, \text{Hz}$ .

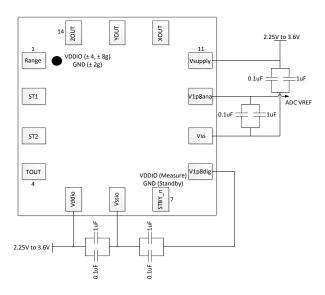

#### **ANALOG OUTPUT**

The ADXL356 application circuit is shown in Figure 13. The analog outputs (XOUT, YOUT and ZOUT) are ratiometric to the internal regulator voltage (V1p8ana) and need to be read carefully in order to achieve the product's inherent noise performance. The zero-*g* bias output is nominally equal to V1p8ana / 2. The recommended option is to use ADXL356 with a ratiometric ADC (e.g. Analog Devices AD7682) with V1p8ana providing the voltage reference. This configuration would result in self-cancellation of errors due to minor supply variations.

The ADXL356 outputs also include 32  $k\Omega$  resistance in series which can be used in conjunction with external capacitors to implement low-pass filtering for antialiasing and noise reduction. The anti-alias filter cutoff frequency should be significantly higher than the desired signal bandwidth. If the anti-alias filter corner is too low, then ratiometricity may be degraded where the signal attenuation is different than the reference attenuation.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. See the last page for disclaimers.

Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

Figure 13. ADXL356 Application Circuit

#### **POWER SEQUENCING**

TBD

#### POWER SUPPLY DESCRIPTION

The ADXL356/ADXL357 has four different power supply domains. The internal analog and digital circuitry operates at 1.8V nominal.

Vsupply: 2.25V-3.6V, input to two low-dropout regulators which generate nominal 1.8V outputs for V1p8ana and V1p8dig.

V1p8ana: All sensor and signal processing circuitry operates in this domain. Offset and sensitivity of the XL354 analog output part are ratiometric to this supply voltage. External ADCs should use V1p8ana as the reference voltage. The ADXL357 digital output part includes A/D converters which are ratiometric to V1p8ana, thereby rendering offset and sensitivity insensitive to the value of V1p8ana. V1p8ana may be the output of an internal regulator, or it may be provided externally.

V1p8dig: This is the supply voltage for the internal logic circuitry. A separate LDO regulator is provided to decouple digital supply noise from the analog signal path. V1p8dig may be the output of an internal regulator, or it may be provided externally.

Vddio: Logic 'high' levels are determined by the value of Vddio. On the ADXL356 analog part, Vddio sets the logic high level for the Self-Test pins ST1 and ST2, as well as the STBY\_n pin. On the ADXL357 digital part, Vddio sets the logic high level for communications

interface ports, as well as the interrupt and DRDY outputs.

The LDO regulators are operational when Vsupply is between 2.25V and 3.6V. V1p8ana and V1p8dig are the regulator outputs in this mode. Alternatively, when Vsupply is tied to Vss, V1p8ana and V1p8dig are supply voltage inputs, with a range of 1.62V-1.98V.

#### **OVER-RANGE PROTECTION**

In order to avoid electrostatic capture of the proofmass when the accelerometer is subjected to input acceleration beyond its full-scale range, all of the sensor drive clocks are turned off. In the  $\pm 10g$  range setting, the over-range protection is activated for input signals beyond  $\pm 40g$  ( $\pm 25\%$ ), and for the  $\pm 20g$  /  $\pm 40g$  ranges the threshold corresponds to  $\pm 80g$  ( $\pm 25\%$ ).

#### **SELF TEST**

The ADXL356 and ADXL357 incorporate a self-test feature that effectively tests their mechanical and electronic systems simultaneously. In ADXL356, the self-test mode can be invoked by driving the ST1 pin to  $V_{\text{DDIO}}$ . Then driving the ST2 pin to  $V_{\text{DDIO}}$  applies an electrostatic force to the mechanical sensor and induces a change in output in response to the force. The self-test delta (or response) is the difference in output voltages between when ST2 is high and ST2 is low, both when ST1 is asserted. After the self-test measurement is complete, bringing both pins low will resume normal operation.

The self-test operation is similar in ADXL357 except ST1 and ST2 can be accessed through the SELF TEST (0x2E) register.

The self-test feature is designed to reject externally applied acceleration and only respond to the self-test force. This allows for an accurate measurement of self-test even in the presence of external mechanical noise.

#### **FILTER**

**TBD**

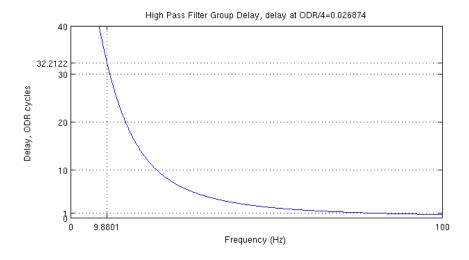

Table 9. Digital Filter Group Delay

|               |        | Dela    | ıy     |        | Atten. |  |  |  |  |

|---------------|--------|---------|--------|--------|--------|--|--|--|--|

|               | SDM    | ODR     |        |        | @ODR/4 |  |  |  |  |

| ODR           | cycles | cycles  | Theory | msec   | (db)   |  |  |  |  |

| 4000          | 161    | 2.52    | 2.50   | 0.63   | -3.44  |  |  |  |  |

| 2000          | 257    | 2.00    | 2.00   | 1.00   | -2.21  |  |  |  |  |

| 1000          | 455    | 1.78    | 1.75   | 1.78   | -1.92  |  |  |  |  |

| 500           | 836    | 1.63    | 1.63   | 3.26   | -1.83  |  |  |  |  |

| 250           | 1605   | 1.57    | 1.56   | 6.27   | -1.83  |  |  |  |  |

| 125           | 3160   | 1.54    | 1.53   | 12.34  | -1.83  |  |  |  |  |

| 63            | 6190   | 1.51    | 1.52   | 24.18  | -1.83  |  |  |  |  |

| 31            | 12184  | 1.49    | 1.51   | 47.59  | -1.83  |  |  |  |  |

| 16            | 24640  | 1.50    | 1.50   | 96.25  | -1.83  |  |  |  |  |

| 8             | 48532  | 1.48    | 1.50   | 189.58 | -1.83  |  |  |  |  |

| 4             | 98383  | 1.50    | 1.50   | 384.31 | -1.83  |  |  |  |  |

| With Interpol | ator   |         |        |        |        |  |  |  |  |

| 64xODR        |        |         |        |        |        |  |  |  |  |

| 256000        | 225    | 3.51661 | 3.50   | 0.88   | -6.18  |  |  |  |  |

| 128000        | 386    | 3.0126  | 3.00   | 1.51   | -4.93  |  |  |  |  |

| 64000         | 705    | 2.752   | 2.75   | 2.75   | -4.66  |  |  |  |  |

| 32000         | 1349   | 2.63459 | 2.63   | 5.27   | -4.58  |  |  |  |  |

| 16000         | 2639   | 2.57732 | 2.56   | 10.31  | -4.55  |  |  |  |  |

| 8000          | 5217   | 2.54725 | 2.53   | 20.38  | -4.55  |  |  |  |  |

| 4000          | 10373  | 2.53257 | 2.52   | 40.52  | -4.55  |  |  |  |  |

| 2000          | 20681  | 2.52452 | 2.51   | 80.78  | -4.55  |  |  |  |  |

| 1000          | 41295  | 2.52045 | 2.50   | 161.31 | -4.55  |  |  |  |  |

| 500           | 82556  | 2.5194  | 2.50   | 322.48 | -4.55  |  |  |  |  |

| 250           | 164963 | 2.51714 | 2.50   | 644.39 | -4.55  |  |  |  |  |

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

ADXL356/ADXL357

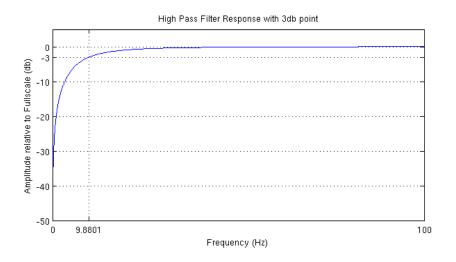

Figure 14 Simulated frequency response of high pass filter with 10Hz cut-off frequency

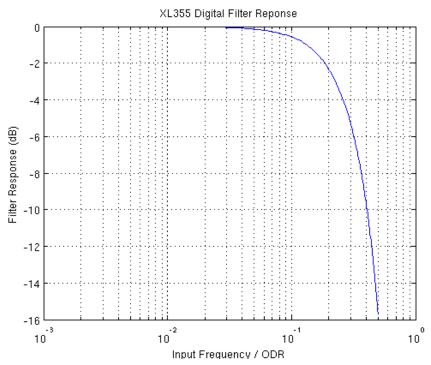

Figure 15 Simulated frequency response of low pass CIC filter with 1kHz corner frequency

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

ADXL356/ADXL357

#### SERIAL COMMUNICATION

The four wire serial interface is designed to communicate in either the SPI or I2C protocol. It will affectively auto-detect the format being used, requiring no configuration control to select the format.

#### **SPI PROTOCOL**

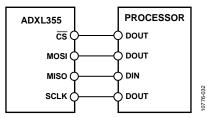

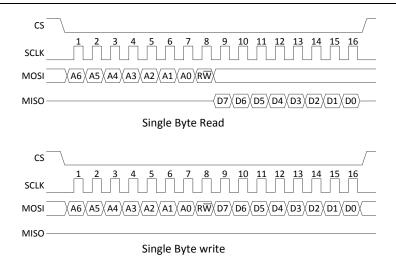

Wire the ADXL357 for SPI communication as shown in the connection diagram in Figure 16. The SPI protocol is summarized in Figure 17. The timing scheme follows clock polarity (CPOL) = 0 and clock phase (CPHA) = 0. The SPI clock speed can range from 100 kHz to 10 MHz.

Figure 16. 4-Wire SPI Connection

Figure 17: SPI Timing Diagram

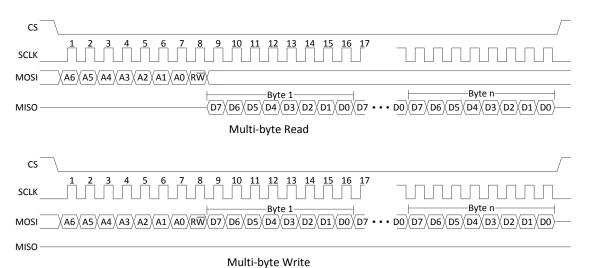

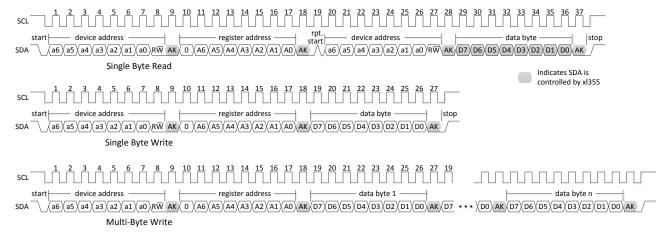

#### I2C PROTOCOL

The I2C protocol is summarized Figure 18. The I2C interface can be used on most buses operating in I2C "Standard mode" (100kHz), "Fast mode" (400kHz), "Fast mode plus" (1MHz), and "High-speed mode" (3.4MHz). The ADXL357 I2C device ID is as follows: ASEL (pin) = 0, device ID = 7'h1D ASEL (pin) = 1, device ID = 7'h53

# READING ACCELERATION OR TEMPERATURE DATA FROM THE INTERFACE

Acceleration data is left justified and with a register address order of most significant data to least significant data. This allows the user to use multi-byte transfers and to take only as much data as he is interested in, either 8 bits, 16 bits, or 20 bits plus marker. Temperature data is 12-bits unsigned, right-justified. The data in XDATA, YDATA, ZDATA, is always the most recent available. It is not guaranteed that XDATA, YDATA, and ZDATA will form a "set" corresponding to one sample point in time. This data set continuity is instead controlled by the routine used to retrieve the data from the device. If data transfers are initiated when DATA\_RDY goes high and completed in a time approximately equal to 1/0DR, then the XDATA, YDATA, ZDATA will apply to the same dataset.

For multi-byte read or write transactions through either serial interface the internal register address will auto-increment. When the top of the register address range, 0x3FF, is reached the auto-increment will stop and not wrap back to the 0x00 address.

The address auto-increment function is disabled when the FIFO address is used. This is so that data can be read continuously from the FIFO as a multi-byte transaction. In cases where the starting address of a multi-byte transaction is less than the FIFO address, the address will auto-increment until the FIFO address is reached and then it will stop at the FIFO address.

Figure 18. I2C Timing Diagram

#### **FIFO**

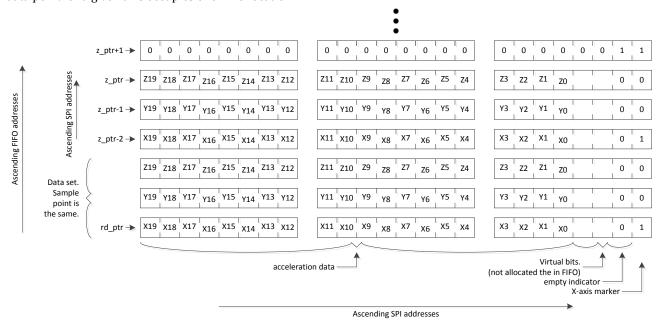

FIFO operates in a stream mode, that is, when the FIFO overruns new data over-writes the oldest data in the FIFO. A read from the FIFO address guarantees that the three bytes associated with the acceleration measurement on an axis all pertain to the same measurement. It is ensured that the FIFO never overruns and data is always taken out in sets (multiples of 3 data points).

There are 96 21-bit locations in the FIFO. Each location contains 20-bits of data and a marker bit for X-axis data. A single-byte read from the FIFO address will "pop" one location from the FIFO. A multi-byte read to the FIFO location will pop the FIFO on the read of the first byte and every third byte read thereafter.

Data is organized in the FIFO as shown in Figure 19. The acceleration data is 2's complement 20-bit data. The two LSBs read on the interface are inserted by the FIFO control logic. Bit 1 is an indicator that an attempt was made to read an empty FIFO, and the data is not valid acceleration data. Bit 0 is a "marker" bit to identify the X-axis, which allows a customer to verify that he is reading FIFO data correctly. An acceleration data point for a given axis occupies one FIFO location.

The read pointer (rd\_ptr) points to the oldest stored data that has not already been read from the interface. There are no physical X-, Y-, Z- acceleration data registers. This data also comes directly from the most recent data set in the FIFO, which is pointed to by the Z pointer (z ptr).

Figure 19. FIFO Data Organization

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

# ADXL356/ADXL357

#### INTERRUPTS

The STATUS register (0x04) contains five individual bits, four of which can be mapped to either the INT1 pin, the INT2 pin, or both. The polarity of the interrupt, active high or active low, is also selectable via the INT\_POL bit in the RANGE (0x2C) register. In general the status register clears when it's read, but this is not the case if the condition which caused the interrupt persists after the read of the register. The definition of "persist" varies slightly in each case, but is described in the following sections. The DRDY pin is similar to an interrupt pin but clears very differently. This case is also described.

#### DATA\_RDY

DATA\_RDY is set when new acceleration data is available to the interface. It is cleared on read of the status register. It will not be set again until acceleration data that is newer than the status register read is available.

Special logic was added to the clear of the DATA\_RDY bit to cover the corner case where new data arrives during the read of the status register. In which case the data ready condition could be missed completely. This logic results in a delay of the clearing of DATA\_RDY of up to four 512 kHz cycles.

#### FIFO FULL

FIFO\_FULL is set when the entries in the FIFO is equal to the setting of FIFO\_SAMPLES. It will clear:

- 1. If the entries in the FIFO falls below FIFO\_SAMPLES. This can only be the case if sufficient data is read from the FIFO.

- 2. On a read of the status register, but only if the entries in the FIFO is less than FIFO\_SAMPLES.

#### FIFO\_OVR

FIFO\_OVR is set when the FIFO is so far over range that data has been lost. The specified size of the FIFO is 96 locations. There is an additional three location buffer to compensate for delays in the synchronization of the clock domains. It is only when there is an attempt to write past this 99 location limit that FIFO\_OVR is set.

FIFO\_OVR is cleared by a read of the status register. It is not set again until data is lost subsequent to this data register read.

#### **ACTIVITY**

ACTIVITY will be set when the measured acceleration on any axis is above ACT\_THRESH for ACT\_COUNT consecutive measurements. An over threshold condition can shift from one axis to another on successive measurements and will still be counted toward the consecutive ACT\_COUNT.

ACTIVITY is cleared on read of the status register, but will be set again at the end of the next measurement if the ACTIVITY conditions are still satisfied.

#### **NVM BUSY**

NVM\_BUSY indicates that the NVM controller is busy with either refreshing the shadow registers, programming the fuses, or running BIST and it cannot generate an interrupt.

NVM\_BUSY is cleared on a status register read that occurs after the NVM is no longer busy.

#### DRDY

DRDY is not a status register bit, but is instead a pin that behaves similar to an unmaskable interrupt. DRDY is set when new acceleration data is available to the interface. It is cleared:

- 1. On a read of the FIFO.

- 2. On a read of XDATA, YDATA, or ZDATA.

- 3. By an auto-clear function that occurs approximately halfway between output acceleration data sets.

DRDY is always active high. It is not affected by the INT\_POL bit field. In EXT\_SYNC modes the first few DRDY pulses after initial synchronization can be lost or corrupted. The length of this potential corruption is less than the group delay.

#### **EXTERNAL SYNC AND INTERPOLATION**

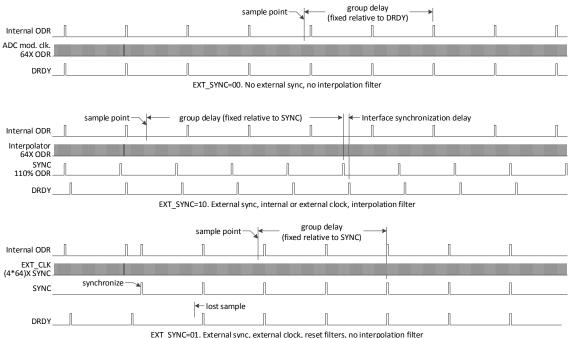

The three proposed external SYNC, interpolation options are shown in Figure 6. For clarity, the clock frequencies and delays are drawn to scale.

"Internal ODR" is the output rate of the decimation filter.

#### Rev PrD

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. See the last page for disclaimers.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

"ADC mod. clk. Is the analog modulator clock rate. The (4\*64)X ODR example is for a 4000Hz ODR. For other ODR\_LPF settings the SYNC frequency approximates the ODR. The relationship to the oscillator clock is modified to: OSC = (4000/ODR)\*(4\*64)\*SYNC. Oscillator clock frequency of 1.024MHz should be used. The oscillator clock must be provided on INT2 pin (Pin 13) and the external SYNC on DRDY pin (Pin 14) as highlighted in Table 8.

Group delay is the digital filter delay from the input to the ADC until data is available at the interface. It is detailed in . This delay is the largest component of the total delay from sensor to serial interface. Figure XX and Figure XX show simulated filter response for the

high pass filter with 10Hz cut-off and low pass filter with  $1 \mbox{Hz}$  corner.

DRDY is an optional output pin.

SYNC is an optional input pin.

#### Table 8. Multiplexing of INT2\_XOUT and DRDY\_ZOUT

| Reg  | ister B         | it Fields             | Pin     | s      |                                                                      |  |  |

|------|-----------------|-----------------------|---------|--------|----------------------------------------------------------------------|--|--|

|      | EXT_            |                       |         |        |                                                                      |  |  |

| EXT_ | SYNC            | INT2_EN               | INT2    | DRDY   |                                                                      |  |  |

| CLK  | [1:0]           | [3:0]                 | Pin 13  | Pin 14 | Comments                                                             |  |  |

| 0    | 00              | 0000                  | LO      | DRDY   |                                                                      |  |  |

| 0    | 00              | not 0000              | INT2    | DRDY   | Internal Cons                                                        |  |  |

| 1    | 00              | 0000                  | EXT_CLK | DRDY   | nternal Sync                                                         |  |  |

| 1    | 00              | not 0000 <sup>2</sup> | EXT_CLK | DRDY   |                                                                      |  |  |

| 0    | 01              | 0000                  | DRDY    | SYNC   | These options will reset the digital filters on every SYNC pulse and |  |  |

| 0    | 011             | not 0000              | INT2    | SYNC   | are not recommended.                                                 |  |  |

| 1    | 011             | 0000                  | EXT_CLK | SYNC   | External Sync, no interpolation filter, data on RDY.                 |  |  |

| 1    | 011             | not 0000 <sup>2</sup> | EXT_CLK | SYNC   | Data represents a sample point "group_delay" earlier in time.        |  |  |

| 0    | 10              | 0000                  | DRDY    | SYNC   |                                                                      |  |  |

| 0    | 10 <sup>1</sup> | not 0000              | INT2    | SYNC   | External Sync, interpolation filter, data on RDY or DRDY. Data       |  |  |

| 1    | 10 <sup>1</sup> | 0000                  | EXT_CLK | SYNC   | sampled "group_delay" earlier in time.                               |  |  |

| 1    | 10 <sup>1</sup> | not 0000              | EXT_CLK | SYNC   |                                                                      |  |  |

#### Notes

- 1 No DRDY

- $\,$  2 No INT2, even though it is enabled.

EXT\_SYNC=01. External sync, external clock, reset filters, no interpolation filt:

Figure 12. External Synchronization Options.

#### EXT\_SYNC=oo. No External SYNC or Interpolation.

This option is shown as a baseline. This example is for ODR\_LPF=0000, the default 4000Hz output rate option. The group delay is shown in **Error! Reference source not found.**.

#### EXT\_SYNC=10. External SYNC with Interpolation.

In this case the internal decimation filter runs exactly as it does in the baseline case, but the user has access to data points between the normal decimation filter outputs. The time resolution of these intermediate points is 1/64\*0DR period. The interface delay shown in Table 10.

Table 10. EXT\_SYNC=10 DRDY Delay

| _       | Delay        |

|---------|--------------|

| ODR_LPF | (osc cycles) |

| 0h      | 8            |

| 1h      | 10           |

| 2h      | 14           |

| 3h      | 22           |

| 4h      | 38           |

| 5h      | 70           |

| 6h      | 134          |

| 7h      | 262          |

| 8h      | 1031         |

| 9h      | 2054         |

| 10h     | 4102         |

# EXT\_SYNC=01. External SYNC with filter synchronization and no interpolation.

With this option the external SYNC is used to synchronize the internal decimation filter such that data is available at the optimum time. There is an initial synchronization of this mode that corrupts the first output data samples that are within one group delay of the EXT\_SYNC (from 1-3). If the restrictions below are

## ADXL356/ADXL357

respected, this corruption happens only once when the SYNC stream begins.

Special restrictions when using this mode are:

- 1. An external clock (EXT\_CLK) must be provided as well as an external SYNC.

- 2. The frequency of EXT\_CLK must be exactly 4\*64x the frequency of SYNC.

- 3. The width of SYNC must be a minimum of 4 EXT\_CLK periods.

4. The phase of SYNC must meet an approximate 25nsec setup time to EXT\_CLK rising edge.

Note that if EXT\_SYNC mode is used and no SYNC is provided, the device will run on its own synchronization. Similarly, after synchronization the device will continue to run synchronized to the last SYNC pulse it received. This means that EXT\_SYNC=01 mode can be used with only a single synchronization pulse.

# Low Noise, High g, Low Power, Low Drift 3-Axis Accelerometer

PRELIMINARY

ADXL356/ADXL357

#### ADXL357 REGISTER MAP

Note: While configuring the ADXL355 in an application, all configuration registers must be programmed before enabling measure mode in POWER\_CTL register. When the part is in measure mode, only the following configurations can be changed: (i) HPF\_CORNER bits in FILTER register, (ii) INT\_MAP register, (iii) ST1 and ST2 fields in SELF\_TEST register, (iv) RESET register.

Table 11, ADXL357 Register Map

| Table | e 11. ADXL3:       | ) / N | egistei             | wap                        |            |       |          |           |          |           |          | ,     |     |

|-------|--------------------|-------|---------------------|----------------------------|------------|-------|----------|-----------|----------|-----------|----------|-------|-----|

| Reg   | Name               | Bits  | Bit 7               | Bit 6                      | Bit 5      | Bit 4 |          | Bit 3     | Bit 2    | Bit 1     | Bit o    | Reset | RW  |

| 0X00  | DEVID_AD           | [7:0] |                     |                            |            |       | DEVID    | _AD       |          |           |          | oxAD  | R   |

| 0X01  | DEVID_MST          | [7:0] |                     |                            |            |       | DEVID_   | MST       |          |           |          | ox1D  | R   |

| 0X02  | PARTID             | [7:0] |                     |                            |            |       | PART     | 'ID       |          |           |          | oxED  | R   |

| oxo3  | REVID              | [7:0] |                     |                            |            |       | REV      | D         |          |           |          | 0X00  | R   |

| 0X04  | STATUS             | [7:0] |                     | RESER\                     | /ED        | NVM   | _BUSY    | ACTIVITY  | FIFO_OVR | FIFO_FULL | DATA_RDY | 0X00  | R   |

| 0X05  | FIFO_ENTRIES       | [7:0] | RESERVE<br>D        |                            |            |       | FIF      | O_ENTRIES |          |           |          | 0x00  | R   |

| oxo6  | TEMP <sub>2</sub>  | [7:0] |                     | RESERVED TEMPERATURE[11:8] |            |       |          |           |          | 0X00      | R        |       |     |

| 0X07  | TEMP1              | [7:0] |                     |                            |            |       | TEMPERAT | URE[7:0]  |          |           |          | 0X00  | R   |

| 8oxo  | XDATA <sub>3</sub> | [7:0] |                     |                            |            |       | XDATA[:  | 19:12]    |          |           |          | 0X00  | R   |

| ox09  | XDATA2             | [7:0] |                     |                            |            |       | XDATA    | 11:4]     |          |           |          | 0X00  | R   |

| охоА  | XDATA1             | [7:0] |                     |                            | XDATA[3:0] |       |          |           | RESER\   | /ED       |          | 0X00  | R   |

| oxoB  | YDATA <sub>3</sub> | [7:0] |                     |                            |            |       | YDATA[:  | 19:12]    |          |           |          | 0X00  | R   |

| oxoC  | YDATA2             | [7:0] |                     |                            |            |       | YDATA    | 11:4]     |          |           |          | 0X00  | R   |

| oxoD  | YDATA1             | [7:0] |                     |                            | YDATA[3:0] |       |          |           | RESER\   | /ED       |          | oxoo  | R   |

| oxoE  | ZDATA <sub>3</sub> | [7:0] |                     | ZDATA[19:12]               |            |       |          |           | 0X00     | R         |          |       |     |

| oxoF  | ZDATA2             | [7:0] |                     | ZDATA[11:4]                |            |       |          |           |          | 0X00      | R        |       |     |

| 0X10  | ZDATA1             | [7:0] |                     | ZDATA[3:0] RESERVED        |            |       |          |           | 0X00     | R         |          |       |     |

| 0X11  | FIFO_DATA          | [7:0] |                     | FIFO_DATA                  |            |       |          |           |          | 0X00      | R        |       |     |

| ox1E  | OFFSET_X_H         | [7:0] |                     |                            |            |       | OFFSET_  | X[15:8]   |          |           |          | 0X00  | R/W |

| ox1F  | OFFSET_X_L         | [7:0] |                     |                            |            |       | OFFSET_  | _X[7:0]   |          |           |          | 0X00  | R/W |

| 0X20  | OFFSET_Y_H         | [7:0] |                     |                            |            |       | OFFSET_  | Y[15:8]   |          |           |          | 0x00  | R/W |

| 0X21  | OFFSET_Y_L         | [7:0] |                     |                            |            |       | OFFSET_  | Y[7:0]    |          |           |          | 0X00  | R/W |

| 0X22  | OFFSET_Z_H         | [7:0] |                     |                            |            |       | OFFSET_  | Z[15:8]   |          |           |          | 0X00  | R/W |

| 0X23  | OFFSET_Z_L         | [7:0] |                     |                            |            |       | OFFSET_  | _Z[7:0]   |          |           |          | 0X00  | R/W |

| 0X24  | ACT_EN             | [7:0] |                     |                            | RESE       | RVED  |          |           | ACT_Z    | ACT_Y     | ACT_X    | 0x00  | R/W |

| 0X25  | ACT_THRESH_<br>H   | [7:0] |                     |                            |            |       | ACT_THRE | SH[15:8]  | ·        |           |          | 0x00  | R/W |

| 0x26  | ACT_THRESH_<br>L   | [7:0] |                     |                            |            |       | ACT_THRE | SH[7:0]   |          |           |          | 0x00  | R/W |

| 0X27  | ACT_COUNT          | [7:0] |                     |                            |            |       | ACT_CC   | UNT       |          |           |          | 0X01  | R/W |

| 0x28  | FILTER             | [7:0] | RESERVE<br>D        |                            | HPF_CORN   | NER   |          |           | ODR_L    | .PF       |          | 0x00  | R/W |

| 0X29  | FIFO_SAMPLES       | [7:0] | RESERVE<br>D        | ESERVE FIFO_SAMPLES        |            |       |          |           | ox6o     | R/W       |          |       |     |